## UNIVERSITY OF THE AEGEAN SCHOOL OF ENGINEERING

### DEPARTMENT OF INFORMATION AND COMMUNICATION SYSTEMS ENGINEERING

## MASTER OF SCIENCE PROGRAMME INTERNET OF THINGS Intelligent Environments in Next-Generation Networks

## A comparative study of programmable switches on modern networking hardware

Master Thesis

of

**Panagiotis Famelis**

Supervisor: Kalligeros Emmanouil, Assistant Professor

Members of the thesis committee: Kambourakis Georgios, Professor Karybali Irene, Ph.D., Laboratory Teaching Staff Member

Samos, July 2023

This page intentionally left blank.

### Acknowledgements

First, I would like to thank Assistant Professor Manolis Kalligeros for the trust he put in me in exploring a relatively new field. Even though the particular subject we worked on was not in his main research interests, his continuous support was fundamental in the completion of this thesis. The same holds true for Dr. Georgios Katsikas, who went above and beyond his duties as a colleague and supported this thesis from conception to completion. Without their guidance and support, this thesis would have been just an idea.

I would also like to thank Dr. Dimitrios Klonidis and the whole NSIT team, with whom I have worked in parallel to this thesis in Ubitech, for their understanding, assistance, and resources they provided. Of course, these acknowledgements would not be complete without the people we walk together in life; my ever-growing family (too many to list them!), my always true friends (D.D., G.D, D.F., M.Z., C.M., G.K. and Clutch) and Despoina who bears with me through life for all these years.

#### © 2023

Panagiotis Famelis Department of Information and Communication Systems Engineering University of the Aegean "O great table, without whom we are as naught." -Most probably no one

## **Table of Contents**

| 1 | Int                                                                                            | roduc                                                                           | ction                                                                                                                                                                                 | 1                                                                   |

|---|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|   | 1.1                                                                                            | Mo                                                                              | dern Computer Networks                                                                                                                                                                | 1                                                                   |

|   | 1.2                                                                                            | The                                                                             | esis Topic                                                                                                                                                                            | 2                                                                   |

|   | 1.3                                                                                            | Stru                                                                            | acture of the Thesis                                                                                                                                                                  | 3                                                                   |

| 2 | The                                                                                            | eoreti                                                                          | ical Background                                                                                                                                                                       | 5                                                                   |

|   | 2.1                                                                                            | Sof                                                                             | tware Defined Networks (SDNs)                                                                                                                                                         | 5                                                                   |

|   | 2.1                                                                                            | .1                                                                              | The Road to SDN                                                                                                                                                                       | 5                                                                   |

|   | 2.1                                                                                            | .2                                                                              | SDN Architecture                                                                                                                                                                      | 6                                                                   |

|   | 2.1                                                                                            | .3                                                                              | Controllers                                                                                                                                                                           | 8                                                                   |

|   | 2.1                                                                                            | .4                                                                              | OpenFlow                                                                                                                                                                              | .11                                                                 |

|   | 2.1                                                                                            | .5                                                                              | P4                                                                                                                                                                                    | .13                                                                 |

|   | 2.2                                                                                            | Pro                                                                             | grammable SmartNICs                                                                                                                                                                   | 23                                                                  |

|   | 2.2                                                                                            | 2.1                                                                             | The Need for SmartNICs                                                                                                                                                                | 23                                                                  |

|   | 2.2                                                                                            | 2.2                                                                             | Network Function Virtualization                                                                                                                                                       | 23                                                                  |

|   | 2.2                                                                                            | .3                                                                              | Programmability of SmartNICs                                                                                                                                                          | 24                                                                  |

|   | 2.3                                                                                            | Stat                                                                            | te of the Art                                                                                                                                                                         | 26                                                                  |

|   |                                                                                                |                                                                                 |                                                                                                                                                                                       |                                                                     |

| 3 | Exj                                                                                            | perim                                                                           | ients                                                                                                                                                                                 | 29                                                                  |

| 3 | Exj<br>3.1                                                                                     | •                                                                               | ents                                                                                                                                                                                  |                                                                     |

| 3 | -                                                                                              | Cor                                                                             |                                                                                                                                                                                       | 29                                                                  |

| 3 | 3.1                                                                                            | Cor<br>. <i>1</i>                                                               | nmon Setup                                                                                                                                                                            | 29<br><i>29</i>                                                     |

| 3 | 3.1<br><i>3.1</i>                                                                              | Cor<br>.1<br>.2                                                                 | nmon Setup<br>Servers                                                                                                                                                                 | 29<br><i>29</i><br><i>30</i>                                        |

| 3 | 3.1<br>3.1<br>3.1                                                                              | Cor<br>.1<br>.2<br>.3                                                           | nmon Setup<br>Servers<br>Metrics                                                                                                                                                      | 29<br>29<br>30<br>31                                                |

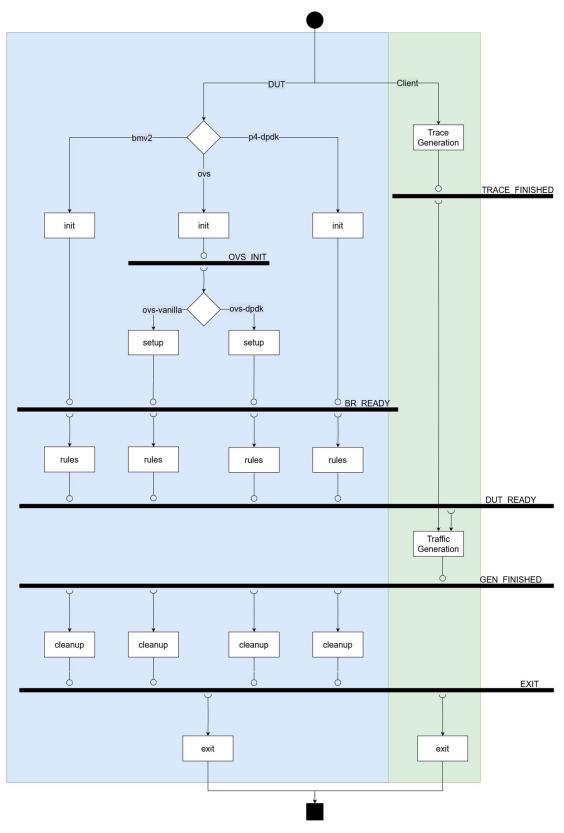

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1                                                                | Cor<br>.1<br>.2<br>.3<br>.4                                                     | nmon Setup<br>Servers<br>Metrics<br>Network Performance Framework                                                                                                                     | 29<br>29<br>30<br>31<br>34                                          |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1                                                  | Cor<br>.1<br>.2<br>.3<br>.4<br>.5                                               | nmon Setup<br>Servers<br>Metrics<br>Network Performance Framework<br>Click Modular Router                                                                                             | 29<br>30<br>31<br>34<br>34                                          |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2                                           | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Ope                                        | nmon Setup<br>Servers<br>Metrics<br>Network Performance Framework<br>Click Modular Router<br>Test Cases                                                                               | 29<br><i>30</i><br><i>31</i><br><i>34</i><br><i>34</i><br><i>34</i> |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2                                           | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Ope                                        | nmon Setup<br>Servers<br>Metrics<br>Network Performance Framework<br>Click Modular Router<br>Test Cases<br>en Virtual Switch (OVS)                                                    | 29<br>30<br>31<br>34<br>34<br>34<br>34                              |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2<br>3.2<br>3.2<br>3.2                      | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Opt<br>.1<br>2.2                           | nmon Setup<br>Servers<br>Metrics<br>Network Performance Framework<br>Click Modular Router<br>Test Cases<br>en Virtual Switch (OVS)<br>OVS and OVS-DPDK                                | 29<br>29<br>30<br>31<br>34<br>34<br>34<br>34                        |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2<br>3.2<br>3.2<br>3.2                      | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Ope<br>2.1<br>.2<br>P4.                    | nmon Setup                                                                                                                                                                            | 29<br>29<br>30<br>31<br>34<br>34<br>34<br>34<br>36<br>37            |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2<br>3.2<br>3.2<br>3.2<br>3.3                      | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Ope<br>.1<br>2.2<br>P4.                    | nmon Setup                                                                                                                                                                            | 29<br>30<br>31<br>34<br>34<br>34<br>34<br>36<br>37                  |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2<br>3.2<br>3.2<br>3.2<br>3.2<br>3.3<br>3.3        | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Ope<br>2.1<br>2.2<br>P4.<br>.1<br>2.2      | nmon Setup<br>Servers<br>Metrics<br>Network Performance Framework<br>Click Modular Router<br>Test Cases<br>en Virtual Switch (OVS)<br>OVS and OVS-DPDK.<br>Experimental Setup<br>Bmv2 | 29<br>30<br>31<br>34<br>34<br>34<br>34<br>37<br>37<br>37            |

| 3 | 3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.1<br>3.2<br>3.2<br>3.2<br>3.2<br>3.2<br>3.3<br>3.3<br>3.3 | Cor<br>.1<br>.2<br>.3<br>.4<br>.5<br>Ope<br>.1<br>2.2<br>P4.<br>.1<br>2.2<br>.3 | nmon Setup                                                                                                                                                                            | 29<br>30<br>31<br>34<br>34<br>34<br>34<br>37<br>37<br>37            |

|     | 3.4.   | 2 SN1000 Plugins                             |

|-----|--------|----------------------------------------------|

|     | 3.4.   | 3 P4 Programs                                |

|     | 3.4.   | 4 Experimental Setup                         |

| 4   | Res    | ults                                         |

| 2   | l.1    | Bmv2                                         |

| 2   | 1.2    | OVS-vanilla                                  |

| 2   | 1.3    | OVS-DPDK                                     |

| 2   | 1.4    | P4-DPDK                                      |

| 2   | 1.5    | Xilinx SN1000 FPGA                           |

| 2   | 1.6    | Remarks on the Comparisons                   |

| 5   | Con    | clusions                                     |

| 4   | 5.1    | Closing Remarks                              |

| 4   | 5.2    | Future Work                                  |

| Bib | liogra | 1phy63                                       |

| An  | nex A  | : P4 program used for Software Switches      |

| An  | nex B  | : P4 program used for Xilinx SN1000's FPGA71 |

## List of Figures

| Figure 1: SDN Architecture according to RFC 7426                       | 7   |

|------------------------------------------------------------------------|-----|

| Figure 2: ONOS Architecture                                            | 9   |

| Figure 3: TeraFlowSDN Release 2 architecture                           | .11 |

| Figure 4: PISA (Protocol-Independent Switch Architecture)              | .14 |

| Figure 5: V1Model Architecture                                         |     |

| Figure 6: PSA Architecture                                             | .15 |

| Figure 7: PNA Architecture                                             | .16 |

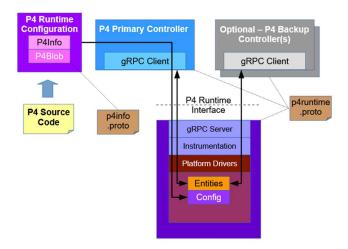

| Figure 8: P4Runtime Reference Architecture                             | .21 |

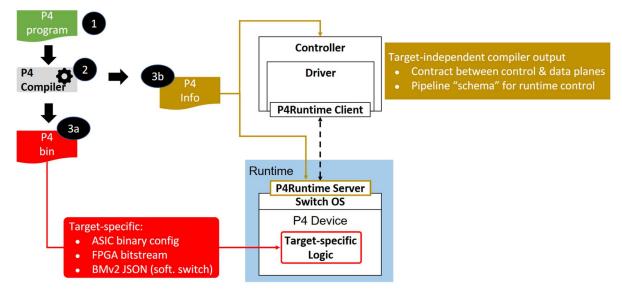

| Figure 9: P4 complete compilation procedure                            | .22 |

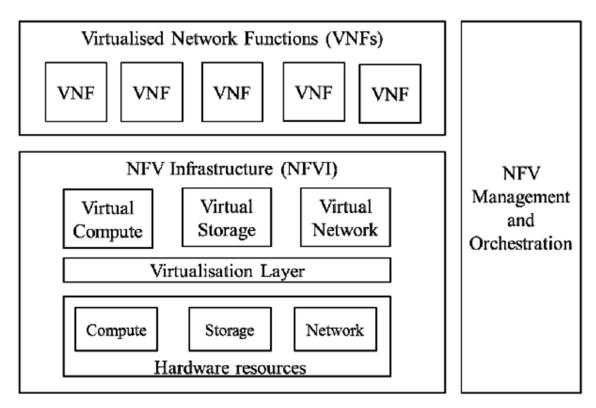

| Figure 10: High-level NFV framework                                    | .24 |

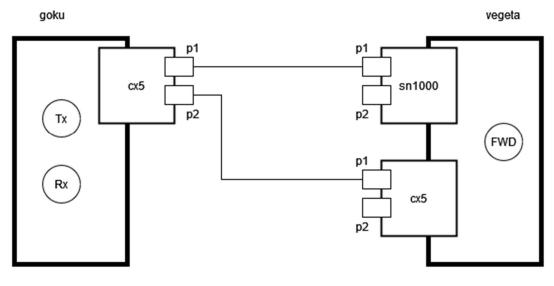

| Figure 11: Server setup                                                | .30 |

| Figure 12: NPF testie flow                                             | .33 |

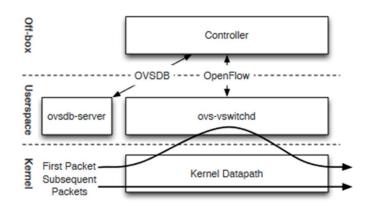

| Figure 13: OVS components and interfaces                               | .35 |

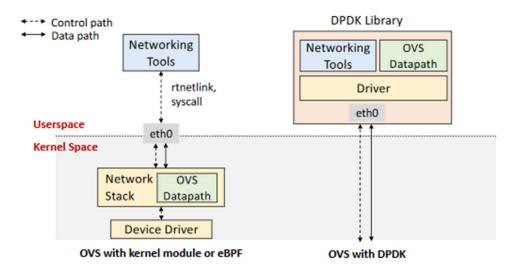

| Figure 14: OVS and OVS-DPDK architecture                               | .36 |

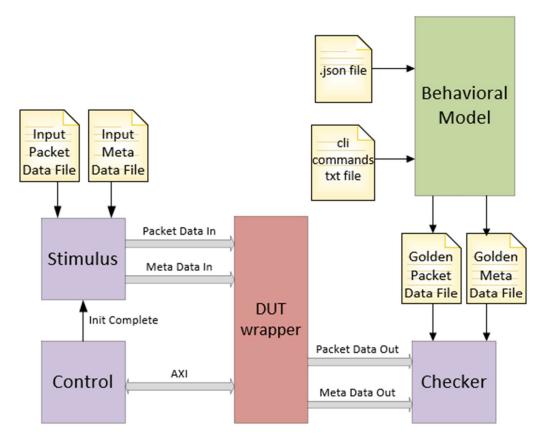

| Figure 15: Testing flow of a P4 RTL                                    | .39 |

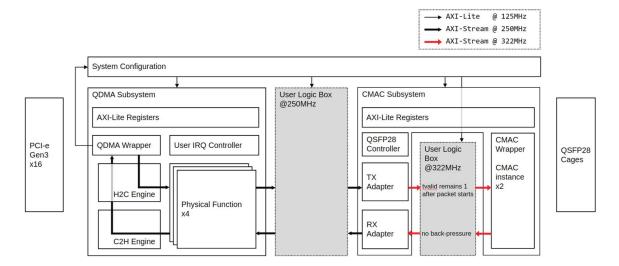

| Figure 16: OpenNIC Architecture                                        | .40 |

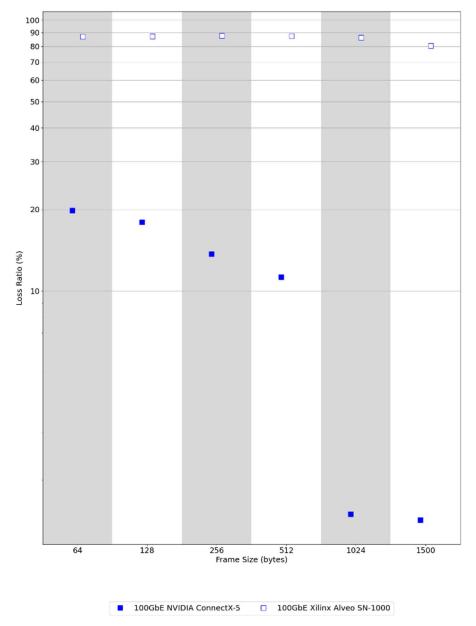

| Figure 17: Loss Ratio graph for bmv2 over different frame sizes        | .43 |

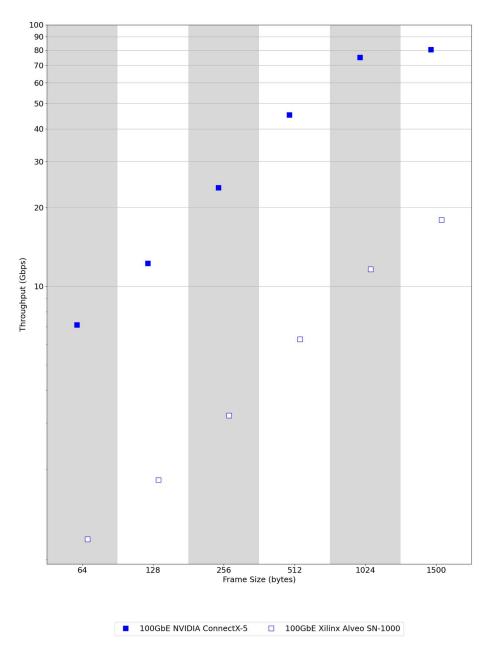

| Figure 18: Throughput graph for bmv2 over different frame sizes        | .44 |

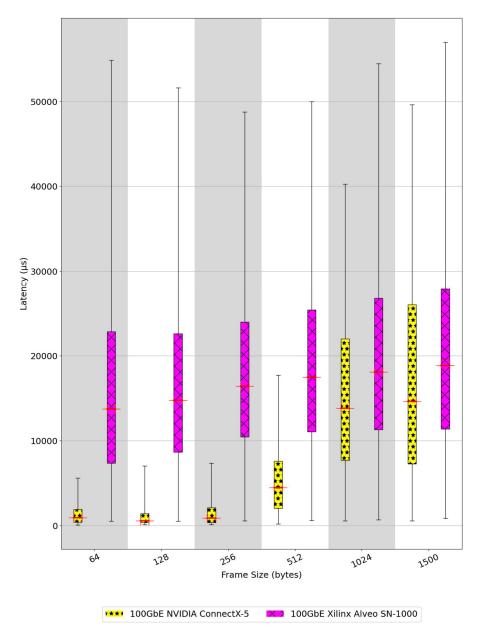

| Figure 19: Latency graph for bmv2 over different frame sizes           | .45 |

| Figure 20: Loss Ratio graph for OVS-vanilla over different frame sizes | .46 |

| Figure 21: Throughput graph for OVS-vanilla over different frame sizes | .47 |

| Figure 22: Latency graph for OVS-vanilla over different frame sizes    | .49 |

| Figure 23: Loss Ratio graph for OVS-DPDK over different frame sizes    | .50 |

| Figure 24: Throughput graph for OVS-DPDK over different frame sizes    | .51 |

| Figure 25: Latency graph for OVS-DPDK over different frame sizes       | .53 |

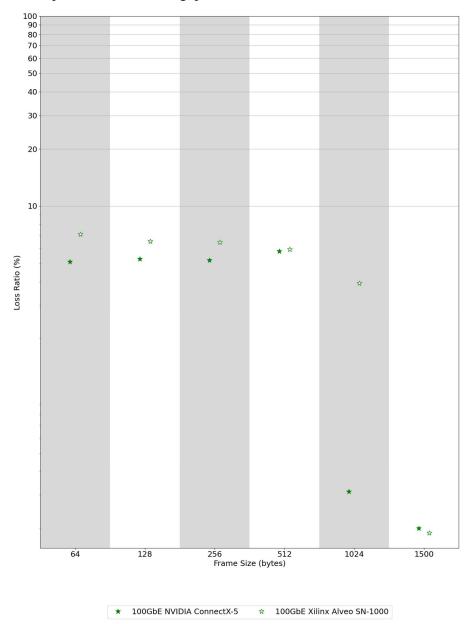

| Figure 26: Loss Ratio graph for P4-DPDK over different frame sizes     | .54 |

| Figure 27: Throughput graph for P4-DPDK over different frame sizes     | .55 |

| Figure 28: Latency graph for P4-DPDK over different frame sizes        | .57 |

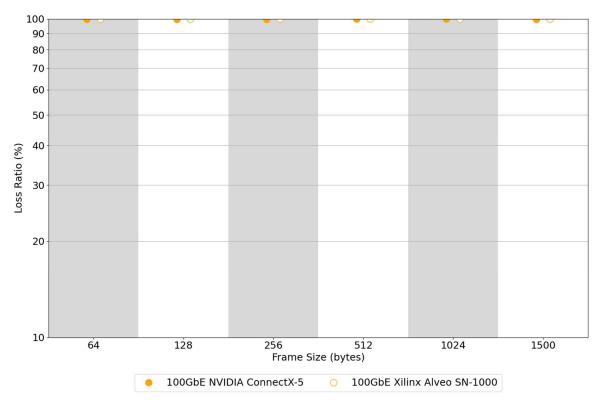

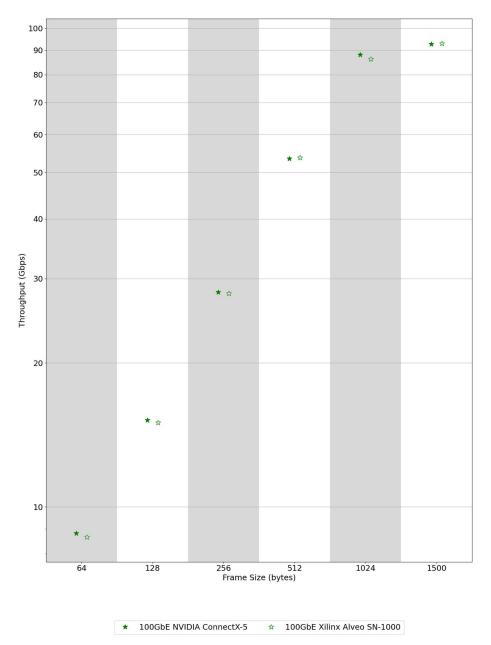

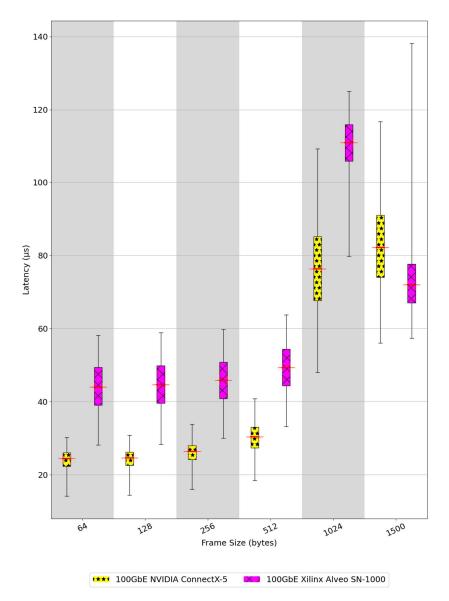

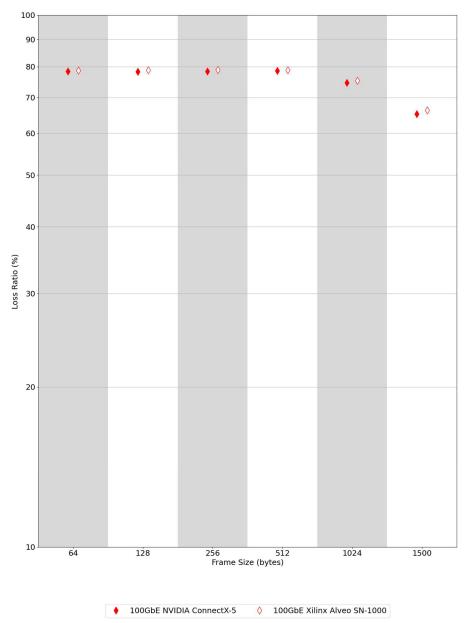

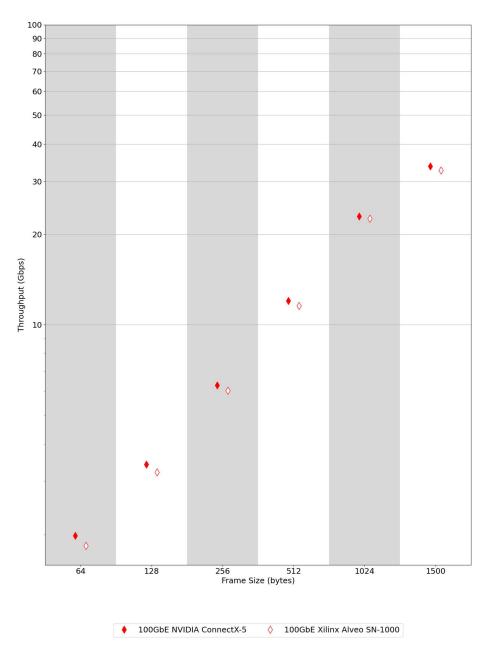

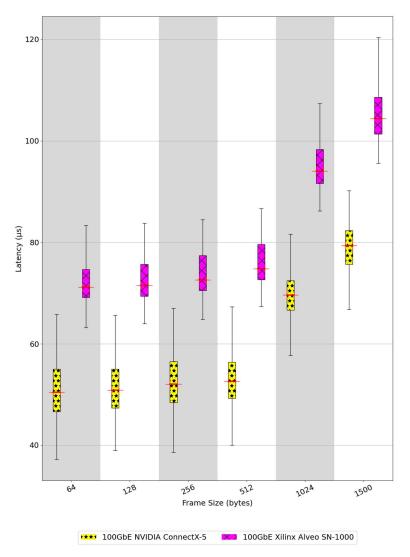

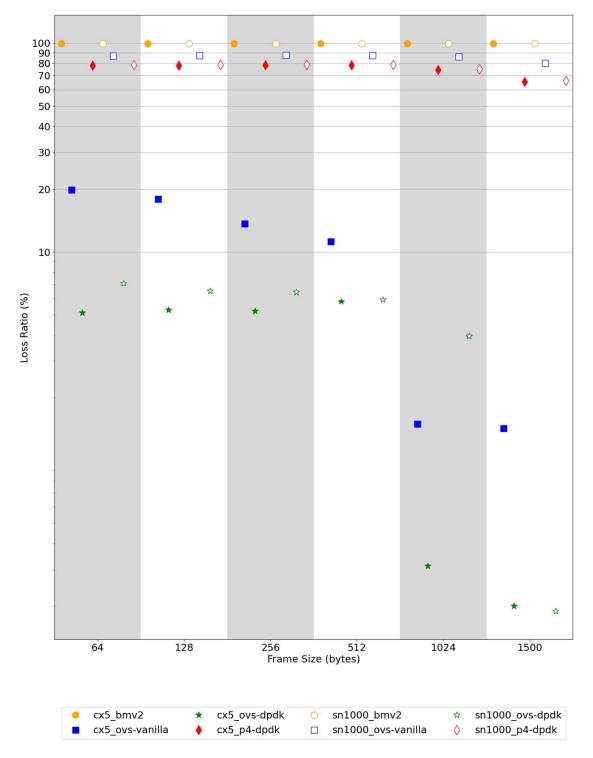

| Figure 29: Comparative results for packet loss                         | .59 |

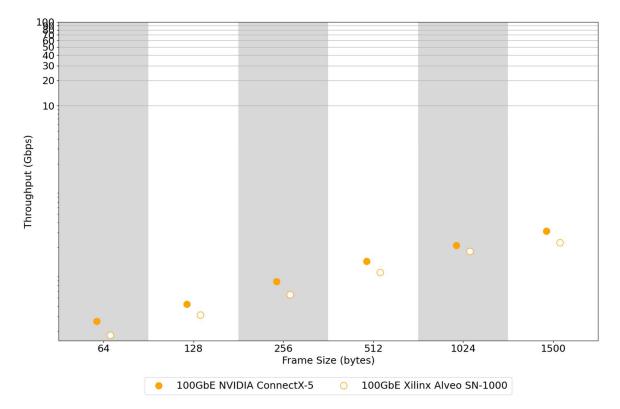

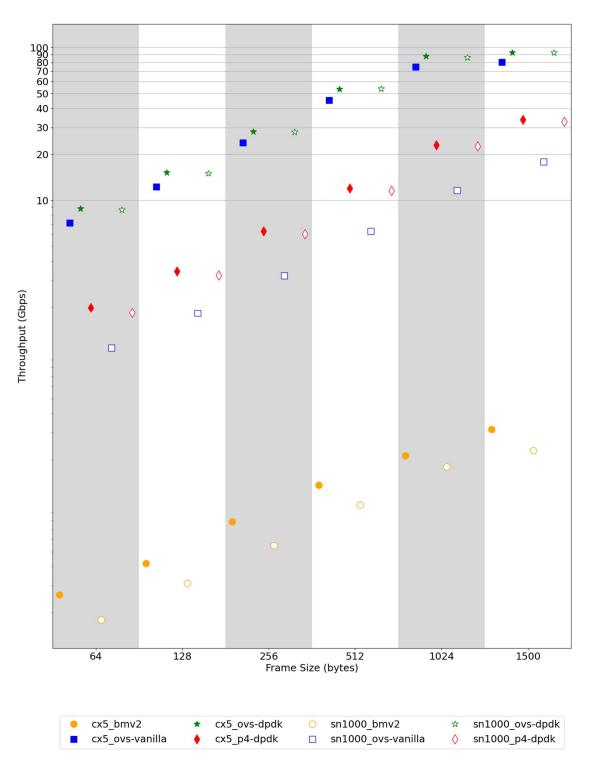

| Figure 30: Comparative results for throughput                          | .60 |

## List of Tables

| Table 1: Server characteristic                             | 30 |

|------------------------------------------------------------|----|

| Table 2: Metrics measured or calculated in the experiments | 31 |

| Table 3: OVS-DPDK parameters                               | 36 |

| Table 4: P4-DPDK EAL parameters                            |    |

| Table 5: bmv2 measurements                                 | 44 |

| Table 6: OVS-vanilla measurements                          | 48 |

| Table 7: OVS-DPDK measurements                             | 52 |

| Table 8: P4-DPDK measurements                              | 56 |

## List of Snippets

| Snippet 1: Ethernet Header                | 17 |

|-------------------------------------------|----|

| Snippet 2: IPv4 Header                    |    |

| Snippet 3: Parser for Ethernet and IPv4   | 18 |

| Snippet 4: Change MAC address example     | 19 |

| Snippet 5: Forward table example          | 19 |

| Snippet 6: Control Block example          | 20 |

| Snippet 7: Conditional apply              | 20 |

| Snippet 8: Deparser for Ethernet and IPv4 | 20 |

| Snippet 9: OpenFlow rule used for OVS     | 36 |

## Abbreviations

| AI      | Artificial Intelligence                         |

|---------|-------------------------------------------------|

| AMD     | Advanced Micro Devices Inc.                     |

| API     | Application Programming Interface               |

| ARP     | Adress Resolution Protocol                      |

| ASIC    | Application-Specific Integrated Circuit         |

| BMV2    | Behavioral Model Version 2                      |

| CDN     | Content Delivery Network                        |

| СРИ     | Central Processing Unit                         |

| CX5     | NVIDIA ConnectX 5 SmartNIC                      |

| DPDK    | Data Plane Development Kit                      |

| DPU     | Data Processing Unit                            |

| DSL     | Domain Specific Language                        |

| DUT     | Device Under Test                               |

| EAL     | Environment Abstraction Layer                   |

| IP      | Intellectual Property                           |

| RTL     | Register-Transfer Level                         |

| ETSI    | European Telecommunications Standards Institute |

| FPGA    | Field-Programmable Gate Array                   |

| gRPC    | gRPC Remote Procedure Calls                     |

| HDL     | Hardware Description Language                   |

| HLS     | High Level Synthesis                            |

| НТТР    | Hyper Text Transfer Protocol                    |

| HW      | Hardware                                        |

| ICMP    | Internet Control Message Protocol               |

| IETF    | Internet Engineering Task Force                 |

| ΙΟ      | Input Output                                    |

| ІоТ     | Internet of Things                              |

| IP      | Internet Protocol                               |

| IPC     | Inter-Process Communications                    |

| IPSec   | Internet Protocol Security                      |

| IRTF    | Internet Research Task Force                    |

| ISP     | Internet Service Provider                       |

| L2 / L3 | Layer 2 / 3                                     |

| LPM     | Longest Prefix Match                            |

| LUT    | Look-Up Table                            |

|--------|------------------------------------------|

| MAC    | Media Access Control                     |

| ML     | Machine Learning                         |

| MPLS   | Multiprotocol Label Switching            |

| NAT    | Network Address Translation              |

| NB     | Northbound                               |

| NFV    | Network Function Virtualization          |

| NIC    | Network Interface Card                   |

| NOS    | Network Operating System                 |

| NPF    | Network Performance Framework            |

| NVMe   | Non-Volatile Memory Express              |

| ONF    | Open Networking Foundation               |

| ONOS   | Open Networking Operating System         |

| OS     | Operating System                         |

| OVS    | Open Virtual Switch                      |

| PC     | Personal Computer                        |

| PCAP   | Packet Capture                           |

| PISA   | Protocol-Independent Switch Architecture |

| PMD    | Poll Mode Driver                         |

| PNA    | Portable NIC Architecture                |

| PNF    | Physical Virtual Function                |

| PSA    | Portable Switch Architecture             |

| QoS    | Quality of Service                       |

| RAM    | Random Access Memory                     |

| RFC    | Request for Comments                     |

| RX     | Receive                                  |

| SB     | Southbound                               |

| SDN    | Software Defined Networking              |

| SN1000 | Xilinx Alveo SN1000 SmartNIC             |

| SNMP   | Simple Network Management Protocol       |

| SR-IOV | Single Root – IO Virtualization          |

| STDIO  | Standard IO                              |

| SW     | Software                                 |

| ТСР    | Transmission Control Protocol            |

| ТХ     | Transmit                                 |

| UDP  | User Datagram Protocol      |

|------|-----------------------------|

| VLAN | Virtual Local Area Network  |

| VM   | Virtual Machine             |

| VNF  | Virtual Network Function    |

| YANG | Yet Another Next Generation |

## Περίληψη

Τα Δίκτυα Καθοριζόμενα από Λογισμικό (Software Defined Networks - SDNs) έχουν αλλάξει ριζικά τον τρόπο με τον οποίο σχεδιάζουμε και διαχειριζόμαστε τα δίκτυα δεδομένων. Με τον διαχωρισμό του επιπέδου ελέγχου (control plane) από το επίπεδο δεδομένων (data plane), πληρέστερα μοντέλα δικτύων μπορούν να αναπτυχθούν. Ενώ έχουν και δυνατότητα προγραμματισμού. Σε αυτό το πλαίσιο εμφανίστηκε και η P4, μια πολλά υποσχόμενη γλώσσα στον τομέα των δικτύων, για προγραμματισμό του επιπέδου δεδομένων. Με τη χρήση της P4 διευκολύνεται η ανάπτυξη και υλοποίηση συγκεκριμένων λύσεων και πρωτοκόλλων προσαρμοσμένων σε ιδιαίτερες ανάγκες και περιπτώσεις χρήσης.

Ταυτόχρονα, η Εικονικοποίηση Δικτυακών Λειτουργιών (Network Function Virtualization -NFV) με την σειρά της άλλαξε τον τρόπο με τον οποίο διαχειριζόμαστε τις δικτυακές λειτουργίες, με μεταφορά πόρων από τους φυσικούς σε εικονικούς. Με αυτόν τον τρόπο επιτυγχάνεται μεγαλύτερη ευελιξία και αποδοτικότητα. Σε αυτό το καινούργιο πλαίσιο, οι μεταγωγείς (switch) υλοποιημένοι σε λογισμικό παίζουν καθοριστικό ρόλο στη δικτύωση των σύγχρονων κέντρων δεδομένων (data centers). Τα switches υλοποιημένα σε λογισμικό μπορούν να τρέχουν είτε στον επεξεργαστή κάποιου εξυπηρετητή (server) ή σε ειδικό υλικό, όπως οι Έξυπνες Κάρτες Δικτύου (smartNICs), οι οποίες είναι βελτιστοποιημένες για να αναλαμβάνουν την εκτέλεση δικτυακών εργασιών.

Για τον λόγο αυτόν, η συγκριτική ανάλυση διαφορετικών switches και smartNICs είναι σημαντική, έτσι ώστε να μπορούμε να ελέγξουμε και να επιλέξουμε τη λύση που ταιριάζει καλύτερα στις ανάγκες κάθε διαφορετικής περίπτωσης. Στο πλαίσιο αυτής της διπλωματικής, συγκρίνουμε τέσσερα διαφορετικά switches, κλασσικού SDN και με P4 (bmv2, OVS, OVS-DPDK, P4-DPDK), σε δύο διαφορετικές κάρτες δικτύου (NVIDIA ConnectX 5 και Xilinx Alveo SN1000) υψηλής ρυθμαπόδοσης (100 Gbps). Ταυτόχρονα, ερευνούμε τον τρόπο με τον οποίο τα προγραμματιζόμενα, σε επίπεδο υλικού, ολοκληρωμένα (Field Programmable Gate Arrays – FPGAs) μπορούν να χρησιμοποιηθούν για να υλοποιήσουν δικτυακές λειτουργίες. Για τον σκοπό αυτό, γράψαμε ένα ειδικό πρόγραμμα σε P4, το οποίο μετατράπηκε σε σχεδιασμό για FPGA μέσα από τα εργαλεία της εταιρείας Xilinx και αξιολογήθηκε.

Λέξεις Κλειδιά: SDN, NFV, smartNIC, P4, OVS, DPDK, FPGA

### Abstract

Software Defined Networks (SDN) have revolutionized the way we design and manage networks. By separating the control plane and the data plane, they allow for better abstractions over the network and enable programmability to allow custom solution. In this context, P4 has emerged as a highly promising, domain specific language for data plane programming, facilitating development and implementation of tailor-made protocols addressing specific needs and use cases.

Simultaneously, Network Function Virtualization (NFV) has transformed network function management, by transitioning from physical to virtual resources, providing flexibility and efficiency. This dynamic landscape has made software switches an integral component of modern data centers and their networks. Software switches can run on the host server's CPU, or on specialized hardware such as Smart Network Interface Cards (smartNICs), optimized for offloading networking tasks.

In this regard, comparisons of different switches and smartNICs is important in order to validate where each solution fits best and pinpoint any problems. In this thesis, we compare four different switches, considering both traditional SDN and P4-enabled SDN solutions (bmv2, OVS, OVS-pdk and P4-DPDK) on two different smartNICs (NVIDIA ConnectX 5 and Xilinx Alveo SN1000) at input rates up to 100 Gbps. Additionally, we investigate how Field Programmable Gate Arrays (FPGAs) can be used to host networking functions. To this end, a special P4 program was also created, converted into an FPGA design using the provided toolchain by Xilinx, and evaluated.

Keywords: SDN, NFV, smartNIC, P4, OVS, DPDK, FPGA

# 1

## Introduction

### 1.1 Modern Computer Networks

Communication networks existed long before the first computers were conceived. From the ancient systems of phryctoriae, pyrseia and hydraulic telegraphs to the more recent electrical telegraphs, people needed a way to communicate across long distances. Modern networks are far more complex and sophisticated than older ones, but the main components are still there: a) a channel- phryctoriae towers had to be visible to their neighbor towers, b) a code- pyrseia operators had to have a common coding system and c) synchronization - hydraulic telegraph operators had to pull the plugs simultaneously. Of course, different physical layers would allow for different and more complex functionalities. This is why for example, the electrical telegraph was able to dominate the world and herald the coming of modern communication networks.

Computer networks, however, allowed for something more. Basically, computer networks merged two branches together, that of communication networks and computer science. By moving from analogue to digital communication, higher abstractions were created. The underlying layer is now bits, an abstraction of the physical world. Due to this, better and more specialized protocols were developed, serving highly specialized purposes, allowing for richer communication and in turn expanding the networks. Eventually, this constant development gave us today's internet.

Yet, richer networks also mean further complexity, in terms of protocols, the ever-expanding network size, the involved hardware, i.e., routers, switches, NICs (Network Interface Cards), etc., and the types of communication, i.e., wired or radio. The innovations in PCs (Personal Computers), laptops and smartphones, allowed more people to connect to the internet. At the same time, the concept of IoT (Internet of Things) emerged, which envisioned the internet as a cyber-physical system. IoT describes the network of various physical entities, called things, which are connected

to the internet. These things collect measurements from their environment and communicate with other things or servers, allowing, in the end, the automation of physical tasks and self-configuration [1]. The increasing number of connected devices and data shared among them proved to be a difficult problem.

To handle this complexity, various management tools and protocols were created, including specific solutions tailored to vendor-locked cases. Also open protocols emerged, like IETF's (Internet Engineering Task Force) SNMP (Simple Network Management Protocol) [2], which became the most famous and de facto management standard for many years. With those tools, operators can connect to entities in an IP (Internet Protocol) network, like routers, monitor their status and configure them. However, that did not change the fact that routers started to become bloated elements, due to their design that needed to support all the various protocols of the internet. At the same time, end-users were becoming more specialized, with specific needs in terms of communication. This meant that on the one hand, not all features of a router were needed, but on the other hand more specialized protocols (like IoT protocols) were developed, which led to more specialized hardware too [3].

The solution can be found not only in creating better management protocols but also in changing the architecture of networks, focusing on alternate ways of controlling and managing the various entities. This gave birth to the notion of SDN (Software Defined Networking), which is a new way of developing and thinking about networks. In SDN, as we will see later in this thesis, networks have a centralized control plane that is programmable with conventional programming techniques and is able to configure the data plane, where the actual switching and routing takes place. Going one step further in this direction, programmable data planes were also introduced, i.e., white-box switching elements that operators are able to program with specific functionalities, allowing tailor-made solutions for their own networks and circumventing the aforementioned bloated software stacks of routers.

More importantly, programmable switches bring a paradigm shift in how we design and implement networks, even more than SDN. P4, the de facto data plane programming language, brings such abstractions that allows a developer to easily create intricate protocols and implement complex functionalities. Moreover, the nature of data plane programmability is interdisciplinary, standing between the areas of networks, systems programming, and hardware development. As we will see later, tools have been developed that allow P4 to serve as an HDL (Hardware Description Language) and produce hardware design for FPGAs (Field-Programmable Gate Array). However, programmable data plane is also a new area, with a lot of innovation and potential use cases, but limited testing and actual implementations. While it is fairly easy to run simulations or emulations of software white-boxes, actual hardware programmable switches and smartNICs are still much more difficult to handle, in terms of price, availability and configuration.

### 1.2 Thesis Topic

The introduction of virtualization technologies migrated the physical servers to VMs (virtual machines), which means that parts of the networking operation also migrated to serve VMs. This led to the introduction of software switches. Networking has also evolved, introducing new

paradigms like programmable data planes. This means that virtual networking should also evolve to reap the benefits of such evolutions. At the same time, the introduction of smartNICs to the modern data center has allowed for increased performance by offloading the networking operations to specialized and programmable hardware.

In this master thesis we engage with exactly the question of measuring the performance of different software switches using different smartNICs as the physical networking elements. We want to compare similar smartNICs in terms of their performance and evaluate whether they would serve the modern needs of data centers and virtualization. For that reason, an NVIDIA ConnectX 5 and a Xilinx Alveo SN1000 smartNICs were used. Both of these cards have the same speed rate of 100Gbps. However, the Xilinx card also includes an FPGA to which hardware can be implemented to quickly serve highly specialized functions.

Simultaneously, we want to check how emerging technologies like P4 programmable software switches stand next to tested and proven solutions. As such we test four different software switches, from simple proof-of-concept ones like bmv2, to production grade switches like OVS and OVS-DPDK, and experimental new switches like P4-DPDK. We test these four switches with a varying number of packet lengths and check their performance in terms of latency and throughput. Additionally, we try to check the FPGA programmability of the Xilinx card using P4 as an HDL, both in terms of performance and ease of use.

In this endeavor, we hope to achieve a dual objective. On the one hand, to come in grip with modern networking concepts and see the methods and technologies involved in designing, building, and managing modern networks. On the other hand, we would like to test certain promising software switches that, to the best of our knowledge, have not been thoroughly tested like P4-DPDK.

### 1.3 Structure of the Thesis

This thesis is organized in five chapters. In Chapter 2 we provide a thorough introduction of the underlying concepts that are required to understand the needs that have arisen in modern networks. In Chapter 3, we detail the experimental setup where we ran our experiments, along with the tools and methods used. In Chapter 4, the results of the experiments are presented along with a discussion on them. Finally in Chapter 5 a recapitulation of our findings from the performed experiments is presented together with some thoughts on future work that this thesis has inspired.

More specifically in Chapter 2, we conduct a comprehensive review of the various changes that happened in the history of modern computer networks. We introduce the notion of Software Defined Networks, their architecture and definitions, along with the most important protocols and controllers. We also review P4, which is, as mentioned the most common programming language used for programming data planes. Furthermore, we discuss the emergence of smartNICs, detailing their applications, programmability, and how they shape today's data centers. We conclude Chapter 2 with a review of the relevant literature in the area, especially that regarding testing of switches and smartNICs.

In Chapter 3, the experimental procedure followed is described. In the first section we discuss about the common setup, and the servers used. Additionally, the common software tools that are present in all the experiments are described. Following, for each experiment we present the software switch under test and the parameters that were used to configure it. A little more detail is provided regarding the Xilinx Alveo SN1000 card, its architecture and the procedure we followed to program its reconfigurable device.

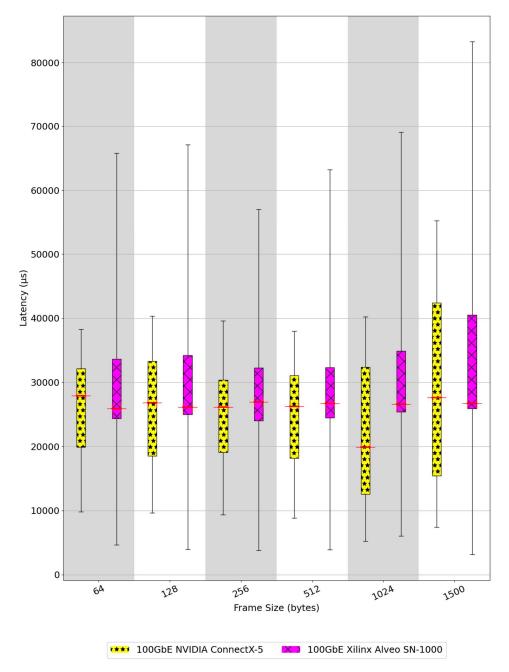

Chapter 4 contains the results acquired from our experiments. The measurements obtained in multiple executions of the tests are presented in diagrams detailing the loss ratio, throughput, and latency for each switch and smartNIC. In this way, a comparative analysis is possible that highlights the differences in behavior among the various switches. We conclude this chapter by describing the difficulties presented in programming and testing the FPGA of the second card.

Finally, Chapter 5 concludes the thesis by recapitulating our findings. Additionally, as we consider this thesis the beginning in a series of work related to programmable networks, we highlight what we believe that possible future work could be and open issues that could be pursued after this.

## 2

## **Theoretical Background**

## 2.1 Software Defined Networks (SDNs)

### 2.1.1 The Road to SDN

One could argue that SDN is one of the most important paradigm shifts that happened in the field of computer networks. Of course, there were earlier attempts to introduce programmability to computer networks. For example, Active Networking in the 1990s was one of the first research projects that paved the way to modern software defined networks. In Active Networks, the operator could send signals to network nodes, along with specific code that had to run on them, essentially changing the behavior of the network programmatically from afar [4].

With the expansion of the internet in terms of data transferred, that kind of in-network processing was starting to seem a good solution for the ISPs (Internet Service Providers), who wanted a way to be able to implement traffic engineering and route traffic in an efficient manner. Traditional distributed routing algorithms, while essential to the operation of any network, lack in terms of ensuring QoS (Quality of Service). However, this kind of programmability was still hard to implement on a large scale, mainly due to the slow adoption rates of innovation by the big telecommunication providers. The solution came with the introduction of OpenFlow Internet protocol in 2008. OpenFlow built on top of the existing TCP/IP (Transmission Control Protocol) suite of protocols, enabling fast adoption to the various operators, while also using slightly modified existing hardware [5]. OpenFlow also marks the first formal introduction of the SDN paradigm as such. For many years SDN was synonymous to OpenFlow, which obfuscated what SDN really is about: is it just some new protocols, is it a new architecture, is it a new way of developing software for networking?

### 2.1.1.1 Separation of Planes

In the heart of SDN lies the distinction between two separate planes of a networking element: the control plane and the data plane (or forwarding plane). The data plane has to do with the functionality of moving data. A switch for example, has the ability to receive data in port 1 and transmit it through another port 2, this is part of the data plane. The control plane on the other hand,

involves how or why this data must go through port 2. This is done through specific rules installed in the switch. Traditional switches and routers encompassed both control and data planes, with the various decisions being made locally using distributed protocols. In SDN, switches and routers are left only with the data plane, i.e., the functionality of transferring data, while the control plane is centralized in a single controller for all the elements in the network. The controller collects data from the switches to learn the state of the network and then makes decisions based on the whole picture. By using what is called a forwarding abstraction, the controller can pass any instructions to the SDN-enabled switches. Forwarding abstractions are well-defined interfaces between controller and the switches, which allow any switch vendor to implement independently and without any restrictions their data plane, provided it can expose and consume that interface. In that way, a controller can operate over a heterogeneous group of switches in a multi-vendor network. In the end, SDN enables not only more efficient routing and switching, but also the implementation of more complex functionalities, like traffic engineering, QoS, NAT (Network Address Translation), firewalls, etc. [6].

### 2.1.2 SDN Architecture

The separation of control plane and data plane is fundamental to the SDN concept. However, just that distinction is not enough to describe the full architecture of an SDN. Following the introduction of OpenFlow, a lot of projects and individual research have enhanced the definition and use cases of SDN. We presented above, the main distinction between data or forwarding plane and control plane. Network engineers started expanding this duality by introducing more layers, like the management layer which concerns the managerial aspects of the control plane (enable/disable ports, etc.), or the application layer, which encompasses all the complex algorithms that may run over the control plane.

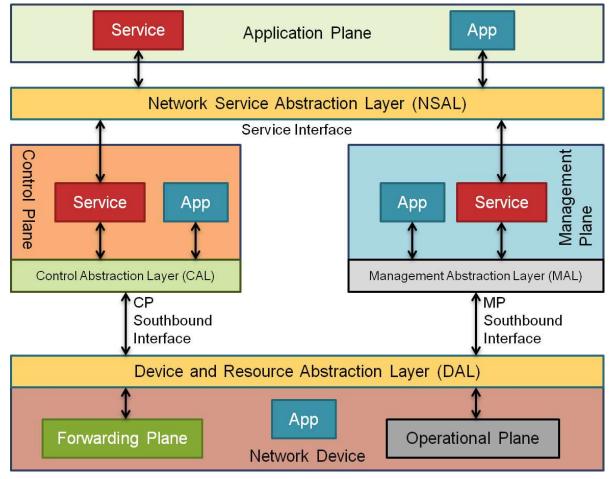

"Software-Defined Networking (SDN): Layers and Architecture Terminology" (RFC<sup>1</sup> 7426) [7] is IRTF's (Internet Research Task Force) attempt to standardize SDN architecture through collecting and consolidating the various ideas that appeared until then. According to RFC 7426, SDN can be fully described by five different planes, going from the infrastructure to higher abstractions (Figure 1):

- 1. Forwarding Plane

- 2. Operational Plane

- 3. Control Plane

- 4. Management Plane

- 5. Application Plane

Mapping to the aforementioned data plane / control plane split, the above variation further splits those two planes according to whether their job involves the function of the network itself (Forwarding and Control planes), or the management of its entities (Operational and Management

<sup>&</sup>lt;sup>1</sup> RFCs stands for "Request for Comments" and correspond to publications of Internet Engineering Task Force, regarding internet operation, protocols, and architecture.

planes). Additionally, it adds another layer, the application plane, which proves to be of great interest.

At the base of the architecture are the network elements, which encompass the forwarding and the operational plane. The forwarding plane contains the functionalities of the data plane, as they were described before, i.e., it is responsible for receiving packets and change, forward, or drop them according to some predetermined rules. The operational plane contains the functionalities that are related to the state of the device, i.e., it is responsible for informing upper planes about the device status (active/inactive), checking and changing if needed, the status of each port (enabled/disabled) and also collecting and exposing monitoring data (temperature, resources utilization, etc.).

Figure 1: SDN Architecture according to RFC 7426<sup>2</sup>

This conceptual separation between network functionality and management of elements is also present in the differences between control plane and management plane. The control plane is responsible for deciding about how different flows should travel throughout the network, what paths they should take in the controlled network and pushing down such configuration to the forwarding plane. On the other hand, the management plane is responsible for monitoring the managed elements and configuring them in terms of their operations. For example, in a scenario of energy efficiency,

<sup>&</sup>lt;sup>2</sup> <u>https://sdn.ieee.org/newsletter/september-2017/overview-of-rfc7426-sdn-layers-and-architecture-terminology</u> (accessed 03/07/2023)

the control plane is responsible for finding energy efficient routes and grooming the traffic to utilize the full bandwidth of a channel. Then the management plane is responsible for finding and turning off the switches or the ports that are not in use anymore, after the changes are pushed down by the control plane.

Before moving on, it is important to note that while forwarding and operational planes, and control and management planes are considered different, their exposed interfaces to the upper and lower levels are common. Essentially this means that the original control plane / data plane dichotomy still exists; control plane encompasses both control and management planes, while data plane encompasses both forwarding and operational planes. A Device and Resource Abstraction Layer (DAL) is considered southbound of the controller to manage and control the data plane, while a Network Service Abstraction Layer (NSAL) is defined northbound, to communicate with high-level applications.

These applications are part of the application plane, which contains all high-level services and algorithms that can be run on a network. These could include complex functionalities like policy and QoS enforcement, running through complex algorithms that could also include ML (Machine Learning) and AI (Artificial Intelligence). It should be mentioned that specific applications can also live in the control and management planes or even in the data plane. However, in that case, the applications should primarily support the basic operation of the network, such as the routing processes, or be involved in automations of the device itself, for example power management.

### 2.1.3 Controllers

This structured architecture is extremely useful as it allowed computer scientists to perceive SDNs like OS (Operating Systems) [8]. The data planes can be understood as computer devices. The control plane communicates with the network entities and provides higher abstractions to northbound applications. In turn, those applications can control the network entities, without having to rely on low level control. That is why the term NOS (Network OS) was coined to also describe the controller. Many controllers were developed over the years, from commercial solutions provided by big technology industries to smaller experimental ones, usually open source, that serve specific use cases. From the second category two solutions seem to be the most interesting in terms of how they influence the research community, in the past and the future: ONOS (Open Networking Operating System) by ONF (Open Networking Foundation) and TeraFlowSDN by ETSI (European Telecommunications Standards Institute).

### 2.1.3.1 ONOS

ONOS is one of the oldest open source SDN controllers, first released in 2014 and written in Java [9]. As an SDN controller it can configure and manage a variety of devices using network management protocols like Openflow, P4Runtime, NETCONF, etc. and provides a NorthBound API (Application Programming Interface) which allows the development of applications that serve a specific purpose. One of its main advantages is the ability to run as a distributed system across different servers.

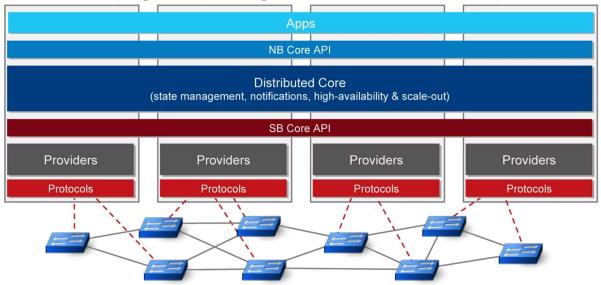

ONOS follows the principles of Code Modularity and Configurability, which mean that the system is extensible with new subsystems or applications and the user has the ability to define which

subsystems are loaded each time. At the same time there is Separation of Concern, with each subsystem having a clear function and Protocol Agnosticism, in the sense that it provides internal abstractions that can handle any southbound protocol in a uniform way. These principles lead to the architecture of Figure 2. Essentially ONOS is a monolithic application comprising of three main components: the Distributed Core, the NB (Northbound) Core API and the SB (Southbound) Core API. The Distributed Core is responsible for storing the network state, providing information to the NB API and configuration to the SB API. The NB Core API exposes specific interfaces, to which applications can adhere and communicate with ONOS, providing higher-level functionalities. The SB Core API, exposes a specific interface, which is consumed by device providers and handles the translation of the abstract models of ONOS to the specific models of each different device (OVS, bmv2, stratum, etc.) or protocol (SNMP, OpenFlow, P4Runtime, NETCONF, etc.)

Figure 2: ONOS Architecture<sup>3</sup>

ONOS is currently used as the basis for most of ONF's projects. As such it has proven to be able to serve many use cases. For example, in SD-RAN<sup>4</sup>, it is shown how ONOS can be used to manage radio resources, while in SD-FABRIC<sup>5</sup>, ONOS is used to control programmable data planes in the edge cloud. All in all, ONOS is a robust, yet complex SDN controller, which has greatly benefitted the SDN community. Unfortunately, even though ONOS has many promising features, it seems that its development has stopped. The main project's github repository has been last updated in August 2022 and the last release (2.7) was in December 2021<sup>6</sup>. This roughly coincides with the acquisition of ONF's development team by Intel. At the same time there is an effort to transition from ONOS to  $\mu$ ONOS, adapting the Distributed Core to microservices. However, the roadmap is

<sup>&</sup>lt;sup>3</sup> <u>https://opennetworking.org/onos/</u> (accessed 29/06/2023)

<sup>&</sup>lt;sup>4</sup> <u>https://docs.sd-ran.org/master/index.html</u> (accessed 29/06/2023)

<sup>&</sup>lt;sup>5</sup> <u>https://opennetworking.org/sd-fabric/</u> (accessed 29/06/2023)

<sup>&</sup>lt;sup>6</sup> <u>https://github.com/opennetworkinglab/onos/tree/master</u> (accessed 29/06/2023)

not clear, as there is still no major release for it and most of the information that can be found is from 2019, when the effort started.

### 2.1.3.2 TeraFlowSDN

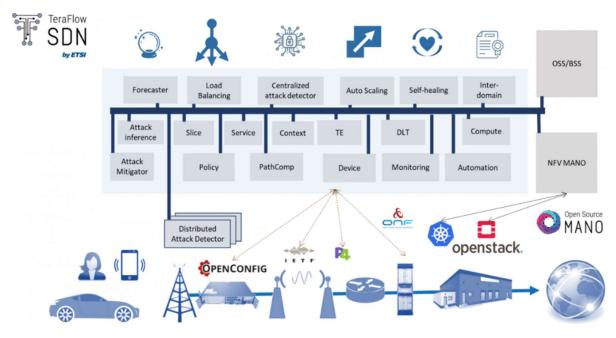

TeraFlowSDN, which emerged from the Horizon2020 research project TeraFlow, is an open source cloud-native SDN controller build around microservices [10]. As such it is distributed by nature, able to auto-scale to serve a large number of flows and devices, and load balance across its different instances. It provides support for a variety of different networks and protocols, including Transport API, NETCONF, gNMI, P4Runtime, and native support for various YANG (Yet Another Next Generation) models, like IETF's microwave elements model.

Following the traditional SDN architecture, TeraFlowSDN comprises of two sets of microservices: the core microservices and overlay netapps. Core microservices include the functionalities that belong to the control and management plane of RFC 7426, while overlay netapps would belong to the application plane. In the heart of the core components is the Context microservice, which keeps all the necessary information for the state of the network, like topology, devices, services, etc.

TeraflowSDN's aim is to be an SDN controller for the whole spectrum of different kind of networks. From the 5G edge, to transport networks and to the IP networks inside a datacenter. For that reason, it follows a model with a single SB interface, the Device microservice, on which different plugins for different kinds of devices can be developed. Over Device, another abstraction is exposed by the Service microservice, which describes a service possibly spanning over different kinds of networks and devices. In that way an operator can describe high level policy requirements in the service level and TeraFlowSDN is able to handle all the necessary configurations at the device level [11].

Similarly, TeraFlowSDN exposes an NB interface to communicate with other systems. This can be used to combine different instances of TeraFlowSDN to form hierarchical controllers and orchestrators, in case, for example, that we need to have different controllers for different domains. Additionally, TeraFlowSDN can cooperate through the NB interface with other systems, like for example ETSI OSM-Open Source MANO (Management and Orchestration), which is able to manage NFV (Network Function Virtualization). The whole TeraFlowSDN architecture is presented in Figure 3.

Figure 3: TeraFlowSDN Release 2 architecture<sup>7</sup>

### 2.1.4 OpenFlow

### 2.1.4.1 OpenFlow Operation

OpenFlow was for a long time the de facto forwarding abstraction, i.e., a protocol that enables the communication between a controller and SDN-enabled devices. There are two types of OpenFlow devices: OpenFlow-only and OpenFlow-hybrid. The first one means that the switch operates only based on the OpenFlow tables, while hybrid means that the switch also supports standard Ethernet operations, like L2 (Layer 2) switching, VLAN (Virtual Local Area Network), L3 (Layer 3) routing, etc. But in both cases, an OpenFlow device contains one or more tables (flow tables) which can contain specific rules (flow entries), installed by the controller. When a packet enters the switch, the switch checks if a flow entry matches with the parameters of the received packet. In this case, the switch executes the related instructions. If no rule matches, a default action can be set by the controller.

While OpenFlow has been discontinued in terms of further developments, it is useful to present how it works, because of its simplicity and how fundamental it is for other newer protocols. According to OpenFlow version 1.5 [12], flow entries consist of the following elements. Note that, except for the Counters field, all the rest of the elements are set by the controller.

- Match fields: specify the information to match the packet.

- Priority: specifies the priority of the specific flow entry. Only the highest priority flow entry that matches the packet will be selected.

<sup>&</sup>lt;sup>7</sup> <u>https://www.teraflow-h2020.eu/blog/upcoming-etsi-teraflowsdn-release-2-features</u> (accessed 29/06/2023)

- Counters: mark how many packets have matched with the specific flow entry. It is automatically updated and not set by the controller.

- Instructions: specify what should be done with the matched packets.

- Timeouts: specify the amount of idle time before the flow is considered expired and removed by the switch.

- Cookie: is an arbitrary value that is chosen by the controller. Its function is to provide a means for the controller to associate extra information with flow rules.

- Flags: alter the way flow entries are managed. For example, the controller can set specific flags in order to also check another table if the flow entry is matched, or remove the flow entry after it matches, etc.

It is obvious that the two most important elements are the Match Fields and Instructions elements. In Match Fields, a controller can request to match the packet based on ingress port, Ethernet and IP types, source and destination MAC (Media Access Control), IPv4 and IPv6 addresses, and source and destination ports of TCP and UDP (User Datagram Protocol). These are the required fields recognized by OpenFlow from its first version. Following versions added more fields as optional, depending on the implementation, like ICMP (Internet Control Message Protocol) fields, ARP (Adress Resolution Protocol) fields, various metadata, etc. It should be noted that the match is not only exact. The controller can request in total four types of matching: exact, wildcard, prefix, and range matching.

Like Match Fields, the Instructions element also defines two different sets of possible actions. One is required to be implemented by any OpenFlow switch, while a second set is optional. The required set allows the selection of egress port, the ability to drop a packet, and the ability to flood it (through the use of groups). The optional set contains various actions mainly related to changes in VLAN and MPLS (Multiprotocol Label Switching) tagging, but also the ability to set a specific value to some field of the packet. That last functionality, while not required by OpenFlow is recommended to be considered as required. Those actions can also be set by the controller as the default action in case no flow entry is matched, as mentioned before.

### 2.1.4.2 OpenFlow Criticisms

OpenFlow was the first major implementation of SDN. As such, it became synonymous with it. Of course, some time was needed until SDN was standardized as something more than OpenFlow, as we will present in the next section. However, during that time, criticism of OpenFlow meant criticism of SDN and vice-versa. The most common criticism had to do with the misconception that if ultimately an SDN switch was to be without control plane, i.e., without the ability to decide where each packet should go, then that would mean that each packet (or at least the first of a flow) arriving on a switch should travel to the controller, which would decide the actions needed and install a new flow entry to the switch, specific for that packet or flow. Of course, this is not true. The controller can install flow entries preemptively and it preconfigure what is to be done with packets that do not match any currently installed flow entries. Ultimately, SDN does not mean that the network could not work without the controller. On the contrary, in many cases, the controller just intervenes when something is wrong, or some special case arises [4].

Another criticism that arose had to do with the centralized nature of SDN. The truth is that collecting the control plane of all the network elements in a centralized silo, the controller, could seem like a security risk. If the controller is lost, so does the whole network. The answer to this criticism has two parts. On the one hand, as mentioned before, the network can continue either by having hybrid switches, which can fall back to non-SDN operation, or by pre-installing correct rules that allow the network to operate with minimal control plane intervention. On the other hand, the fact that the SDN proposes a centralized architecture does not mean that the controller itself is centralized. The controller can be, and most probably is, distributed in nature [13]. Its functions are logically centralized, but the controller can be physically distributed, running across different servers. The exact relationship between the controller's various instances are up to each specific implementation. If for example they use a hierarchical or swarm model, but in a correctly built network, the controller should be able to always fall back to a live running instance.

### 2.1.5 P4

As the SDN concept was evolving, OpenFlow's development stumbled upon some questions: Can OpenFlow, as the de facto SDN implementation, keep up in terms of elements supported? Can we continue to have fixed tables and fields that flows can match to? Or, maybe, we need more flexibility on how we define both the functionality of the data plane and its management?

The above questions led to what came to be the new standard for SDN, the P4 programming language [14]. P4 stands for Programming Protocol-independent Packet Processors and is a DSL (Domain Specific Language), which can be used for data plane programming. The idea of having programmable switches was not new. For example Click modular router [15] had already been proposed, as a way to define specialized software switches. However, P4 was designed with the control plane in mind, encompassing the full SDN paradigm and with the aim of evolving into an OpenFlow 2.0. The programmer can use P4 to define the pipeline of a switch. This is done by defining parsers of protocols. The switch can understand and define specific match-action tables that it will use to act on each incoming packet. The match-action tables are defined in such a way that allow a control plane to control the switch functions. This is done through an API, called P4Runtime, that is generated at compile time and defines all the possible actions and instructions the controller can use to instruct the switch.

Before describing in detail the internals of the P4 language, it is important to note the significance of it. While SDN changed the way we see and design networks, P4 went one step further, unlocking the full potential of the paradigm shift that takes place. In the history of programming languages there are two main points that accelerated the evolution of the field. The introduction of assembly language, which allowed programmers to write readable code and the introduction of high-level languages, which allowed programmers to reason about code. The introduction of P4 bears the same significance. If protocols are like assembly, readable but cumbersome, leading easily to ossification, P4 is the high-level language for networks, allowing the development of tailor-made protocols for each network, with flexibility and agility in their deployment [16]. We are still in the midst of this revolution and cannot foresee how it will evolve, but P4 can act as the bridge between the fields of network and software engineering. This is not only beneficial in terms of what we can describe, or how we can offload parts of programming to the

network itself, but more importantly, it means that networks can be formally verified and not depend on the implementation of some specific protocol [17].

### 2.1.5.1 P4 Architectures

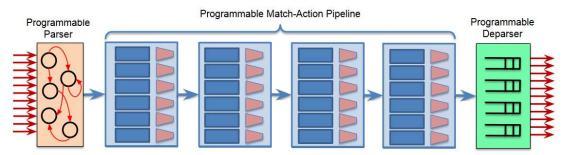

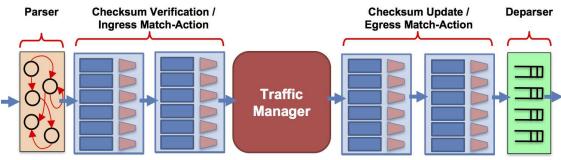

At the heart of P4 lies PISA (Protocol-Independent Switch Architecture), as shown in Figure 4. PISA comprises of three basic building blocks:

- Programmable Parsers

- Programmable Match-Action Pipeline

- Programmable Deparsers

Through the programmable parser, the developer can define the protocols that their data plane will recognize and use. Like in OpenFlow, packets pass through a series of tables, the programmable match-action pipeline, where the packets are altered, routed, dropped, or stored based on specific conditions. Finally, the developer is also able to declare the programmable deparser, defining how the output packets will look in the wire.

Figure 4: PISA (Protocol-Independent Switch Architecture)<sup>8</sup>

In its most simple architecture, PISA can look like Figure 4, i.e., an incoming packet would first go through a parser, then continue to one or more match-action tables and finally arrive at a deparser before going out the switch. However, one could think of different setups. First of all, special non-programmable blocks can also be included. These blocks are called externs in P4 and have some fixed function they are serving. Additionally, the order of the various blocks is not fixed. Most probably, a parser is needed at the beginning and a deparser at the end of the pipeline, but in the middle all four blocks can exist in various setups to better specific needs or different hardware designs. For example, one could argue for an architecture that would first parse some specific protocol, decide through a table on it and if the packet were to continue, then parse the inner protocols. That would mean that the architecture would have pairs of one parser and match-action tables in a row.

P4 has two main versions:  $P4_{14}[18]$  and  $P4_{16}[19]$ . In  $P4_{14}$ , the V1Model (Figure 5) was the standard architecture used. In it two different sections are defined; an Ingress, comprised of a parser and some match-action tables that are used, among other things, to verify the checksum of the incoming packet, and an Egress, comprised of some math-action tables, that among other things, can update the checksum of the packet to be sent out of the switch, and a deparser to serialize the

<sup>&</sup>lt;sup>8</sup> <u>https://opennetworking.org/wp-content/uploads/2020/12/P4\_tutorial\_01\_basics.gslide.pdf</u> (accessed 30/06/2023)

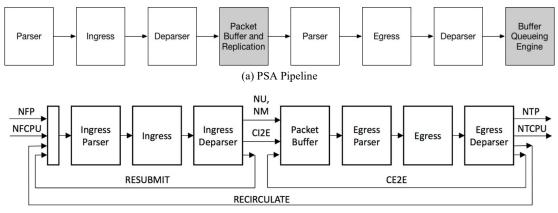

packet. In-between, the Traffic Manager extern is present that queues the packets and assigns priority if needed. V1Model was deprecated in P4<sub>16</sub>, which introduced two new standard architectures: PSA (Portable Switch Architecture) [20] and PNA (Portable NIC Architecture) [21].

Figure 5: V1Model Architecture<sup>9</sup>

PSA [Figure 6(a)] is the evolution of the V1Model. Like previously, two sets of pipelines are defined, Ingress and Egress. Both have a parser, some match-action tables and a deparser. Inbetween a Packet Buffer and Replication Engine exists, which is responsible for queuing and replicating packets if needed (for example in the case of multicast). Also, at the end, a Buffer Queueing Engine is present that queues the packets and can also forward them to the CPU (Central Processing Unit). In Figure 6(b), the various paths a packet can take are presented. It can be seen that while PSA is similar to V1Model, it is much more flexible, allowing for better recirculation and handling of multicast packets.

#### Figure 6: PSA Architecture [20]

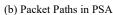

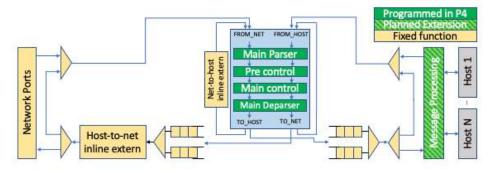

Previous architectures were designed to be used mainly by switches. However, as we will see later, P4 can also be used to program other kinds of data planes, like smartNICs. This led to the design of another standard architecture. PNA (Figure 7) is the architecture of an abstract smartNIC, as such its design is more specific, taking into account functionalities that are usually found in NICs, like encryption/decryption. It should also be noted that it is still a work in progress, which is why planned extensions are present in Figure 7.

<sup>&</sup>lt;sup>9</sup> <u>https://forum.p4.org/t/p4-architecture/246/2</u> (accessed 01/07/2023)

PNA's, programmable parts are fewer than PSA, reminding the original PISA. It consists of a parser, two blocks of match-action tables (Pre control and Main Control) and a deparser. Additionally, other than the ports and the queuing systems, two main externs are defined: Net-to host and Host-to-net. These two are used mainly for functionalities that have to do with the network the host is attached to. For example, in the case of IPsec (IP Security), the authentication and decryption of the incoming packets would be the responsibility of the Net-to-host inline extern, while the signing and the encryption would be the responsibility of the Host-to-net inline extern. Because of this particularity arises the need for the Pre control programmable block, which is responsible for checking that the incoming packet is signed in a correct way and needs to be sent to the Net-to-host inline extern. In this case, the packet passes the programmable pipeline, going to the extern for authentication and decryption and then is recirculated again to the programmable pipeline. If the packet was not signed correctly, the pre control would drop it immediately, without circulating further. On the other hand, Main control, has the complete functionality the developer would want to implement on the smartNIC.

Figure 7: PNA Architecture [21]

PSA and PNA are the two standard architectures defined by the P4 consortium. However, vendors are free to conform to those two or define their own architectures that suit their needs. For example, Xilinx uses their own custom architecture, which is a modified V1Model, presented in chapter 3. Of course, the externs in different architectures could be different, which is why it is recommended to use the standardized externs in the P4 library, but the programmable parts of a P4 program are highly reusable. When writing a P4 program, the developer defines different blocks and at the end, matches those blocks to the architecture provided. This modularity in P4 programs enables greater code reuse, as a P4 program written for one architecture would need mostly rearrangements to comply to other architectures.

### 2.1.5.2 P4 Language

P4 is a programming language, specific to the domain of data plane programming. However, that does not mean that it is not a complete language, with its own grammar and syntax. Inspired by C, it looks like it, but it is a DSL and as such, it has specific statements, limited to the needs of network programming; for example, there is no loop (for or while) statement to be used in P4. The full formal description of the language can be found in the P4<sub>16</sub> language specification [19], from which the following short, informal description has been extracted.

A typical P4 program contains three main components:

- 1. Header definition

- 2. Parser logic

- 3. Control Blocks

#### 2.1.5.2.1 Header

In the header definition, a programmer defines the structure of the header of the protocols that they want to use. For example, the Ethernet frame headers and IPv4 headers are shown in Snippet 1 and Snippet 2 respectively.

| header Ethernet | _h {                |

|-----------------|---------------------|

| <b>bit</b> <48> | dstAddr;            |

| <b>bit</b> <48> | <pre>srcAddr;</pre> |

| <b>bit</b> <16> | etherType;          |

| }               |                     |

#### **Snippet 1: Ethernet Header**

| <pre>header IPv4_h {</pre> |                        |

|----------------------------|------------------------|

| <b>bit</b> <4>             | version;               |

| <b>bit</b> <4>             | ihl;                   |

| <b>bit</b> <6>             | dscp;                  |

| <b>bit</b> <2>             | ecn;                   |

| <b>bit</b> <16>            | totalLen;              |

| <b>bit</b> <16>            | identification;        |

| <b>bit</b> <3>             | flags;                 |

| <b>bit</b> <13>            | <pre>fragOffset;</pre> |

| <b>bit</b> <8>             | ttl;                   |

| <b>bit</b> <8>             | protocol;              |

| <b>bit</b> <16>            | hdrChecksum;           |

| <b>bit</b> <32>            | <pre>srcAddr;</pre>    |

| <b>bit</b> <32>            | dstAddr;               |

| }                          |                        |

#### Snippet 2: IPv4 Header<sup>10</sup>

Basically, a header definition is a traditional structure which describes all the fields of the protocol. The sequence of the fields is important, because the header is parsed sequentially and it is mapped based on the order of the definition. Also, the headers themselves, as structures, can be used in defining other structures, such as sets of packets to be parsed. In fact, it is needed to define what kind of header combinations are acceptable by the parsers. Again, the sequence is important.

<sup>&</sup>lt;sup>10</sup> Note that the IPv4 headers defined here, do not have the Options field. This is omitted here for simplicity. The Options field has variable and not constant length. As such, for the definition, one would have to use the varbit keyword and parse the headers with care.

## 2.1.5.2.2 Parser Logic

After defining the protocols a P4 program uses, a programmer should define the parsers to be used. Parsers are basically state machines, with each state usually representing one protocol header and the transitions to other protocol headers in simple programs. In more complex programs, transitions could be used to implement loops or change between different options inside a protocol header.

In Snippet 3, a simple parser for the above Ethernet and IPv4 is shown. There should always be a start state, from which the state machine should begin. Then the header fields are extracted and stored in some header variables. It is possible to also extract only parts of the header. Based on the extracted values, transitions are defined that look similar to the switch statement in C. Like the special start state, two more special states are defined: accept and reject, which mark the parsed packet as ready to move on to the next block, or to be dropped. In case no transition is mentioned on some block, the reject transition is considered the default one. While it may seem like fields must be first fully parsed in order to be used, various functionalities are available that can be used to look ahead to some field, not yet fully parsed, etc.

```

parser MyParser(packet in pkt, out accepted packet hdr) {

Checksum16() cksum;

state start {

pkt.extract(hdr.ethernet);

transition select(pkt.ethernet.etherType) {

// If the value of etherType is 0x0800

// transition to parse ipv4

// else drop (implicit)

0x0800: parse ipv4;

}

}

state parse ipv4 {

pkt.extract(hdr.ip);

cksum.clear();

cksum.update(hdr.ip);

// check that checksum is 0, else raise an error

verify(cksum.get() == 16w0, error.IPv4ChecksumError);

transition accept;

}

}

```

#### **Snippet 3: Parser for Ethernet and IPv4**

In Snippet 3, the keyword "out" is shown. P4 defines 3 kinds of directions that define whether a parameter can be written or not: *in*, *out*, *inout*. Read-only parameters are marked by *in* and are initialized by copying the value of the corresponding argument. *out* marks that the parameter is uninitialized and after the execution of the call, the value will be copied to the corresponding variable. Finally *inout* means that the initial value is copied from the corresponding argument and it will be updated after the execution ends. If a parameter is not marked by such a keyword, it means that it is set by the control plane, or it is known at compile-time, or it is set by another calling block, in which case it is implied as an *in* parameter.

#### 2.1.5.2.3 Control Blocks

Control blocks are used for both Match-Action processing and deparsing. A control block has three basic parts: Actions, Tables and application. An action looks like an imperative function with no return value. It consists of some Action Code and some Action Data. The first is set by the P4 program, while the second is set by the control plane. For example, in Snippet 4, the mac addresses of the packet are changed. The new source address is taken from the old destination address and the new destination address is set by the controller. Action data is the new source address, while the rest is action code. Inside an action only statements and declarations are allowed, with no switch or if statements. What that means is that an action will just apply what is defined in it every time. All conditional checks should be done one level higher, on the level of tables.

```

action set_mac(bit<48> new_dst_addr) {

hdr.ethernet.srcAddr = hdr.ethernet.dstAddr;

hdr.ethernet.dstAddr = new_dst_addr;

}

```

#### Snippet 4: Change MAC address example

More important is the table part. As mentioned before, tables are the main mechanism in OpenFlow, through which the controller influences the data plane. The same structure has been kept in P4 too. Like in OpenFlow, a table should contain different entries. However, in P4, we describe the schema of the table and not the entries themselves. A table has two main properties: keys and actions.

A key is an expression that describes the parameters that are going to be used for look-up in the table. It consists of a definition of what kind of header fields can be defined and also the type of matching. P4 supports three kinds of matching: exact, ternary and lpm. Exact looks for the whole value in the key, ternary uses both a value and a mask for that value, while lpm (longest prefix match) is similar to ternary but checks only for the prefix of a value. Note that a key can be a combination of different fields. In Snippet 5, for example the key is set as the source mac address of the packet with exact matching.